چینیها با موفقیت یک پردازنده با ۲۵۶ هسته تولید کردهاند و اعلام کردهاند که قصد دارند به همین طراحی ادامه داده و یک تراشه با ۱۶۰۰ هسته را تحت چارچوب یک تراشه یکپارچه تولید کنند. پژوهشگران چینی تراشه ۲۵۶ هستهای خود را با نام “Zhejiang Big Chip” معرفی کردهاند و قصد دارند مدل ۱۶۰۰ هستهای را با طراحی یکپارچه در ابعاد یک ویفر ارائه دهند. هنوز مشخص نیست که قیمت این پردازنده در این ابعاد چقدر خواهد بود.

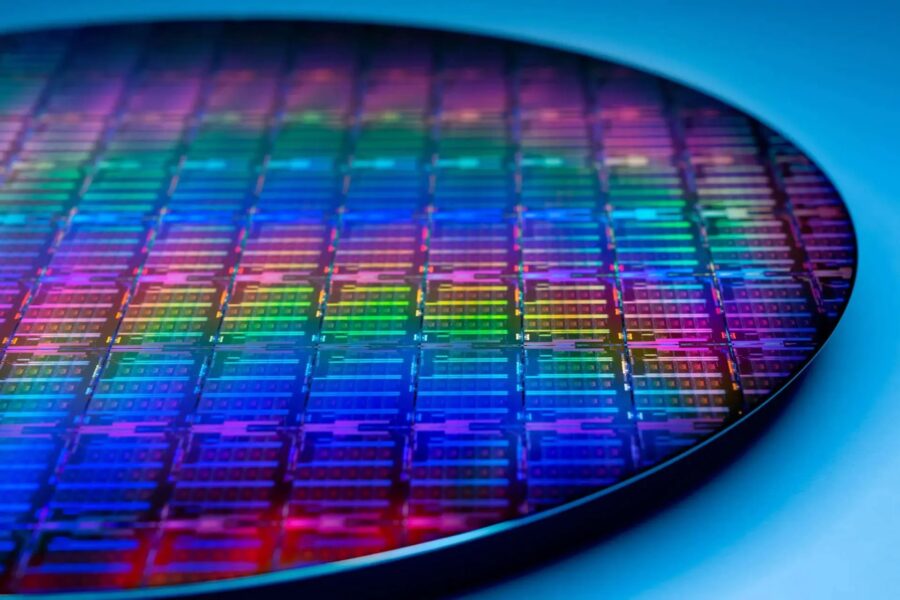

در زمینه توسعه تراشهها، افزایش چگالی ترانزیستورها در نسلهای جدید دشوارتر شده است. به همین دلیل، تولیدکنندگان به دنبال راههای جدید برای افزایش عملکرد پردازندهها میگردند. این راهها شامل نوآوری در معماری، بزرگتر کردن ابعاد تراشه، طراحی چیپلتهای چندگانه و تراشههای با ابعاد ویفر (Wafer Scale) میشود.

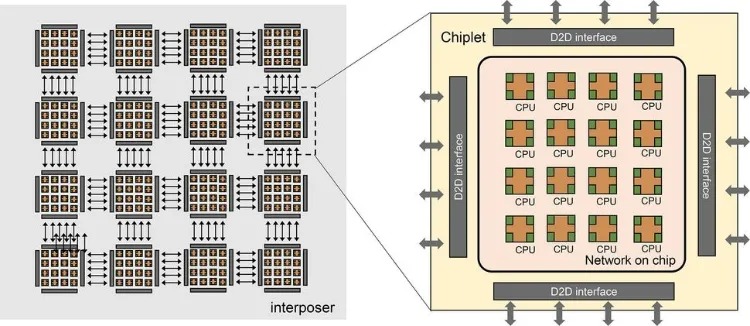

تا به حال، تنها شرکت Cerebras آمریکا موفق به ساخت تراشههای Wafer Scale شده است. اما بهنظر میرسد که توسعهدهندگان چینی نیز به این روش توجه دارند و در حال حاضر به طراحی چیپلت چندگانه با ۲۵۶ هسته پرداخته و راههایی برای رسیدن به مقیاس ویفر را بررسی میکنند. بر اساس یک مقاله تحقیقاتی جدید، تراشهای که محققان چینی طراحی کردهاند، ۱۶ چیپلت دارد و هرکدام از این چیپلتها دارای ۱۶ هسته با معماری ریسک-۵ هستند. این هستهها به روش پردازندههای چندگانهی متقارن (SMP) به یکدیگر متصل شدهاند و از طریق اتصال شبکه-روی-چیپ قادر به به اشتراک گذاری حافظه میباشند. پژوهشگران باور دارند که این طراحی قابل مقیاسپذیری برای ۱۰۰ چیپلت یا ۱۶۰۰ هسته را فراهم میکند.

هر ۱۶ هسته یک چیپلت و ۱۶ چیپلت مرتبط با هم

چیپلتهای Zhejiang با استفاده از فناوری ۲۲ نانومتری SMIC، که بزرگترین شرکت تراشهساز چین، تولید شدهاند. در حال حاضر، مقدار دقیق انرژی مصرفی برای ساختار ۱۶۰۰ هستهای مبتنی بر لیتوگرافی ۲۲ نانومتری مشخص نیست.

پژوهشگران اظهار داشتهاند که چیپلتهای چندگانه میتوانند به عنوان یک راهحل قدرتمند و انعطافپذیر برای ساخت پردازندههای مورد استفاده در ابرکامپیوترها بهکار گرفته شوند؛ روشی که در حال حاضر در برخی از مدلهای پردازنده AMD و اینتل نیز بهکار میرود.

در مقالهی خود، پژوهشگران ذکر کردهاند: “برای محاسبات اگزا مقیاس (قدرت پردازش بیش از یک اگزا فلاپس) فعلی و آینده، معماری چیپلت سلسلهمراتبی را بهعنوان یک راهحل قدرتمند و انعطافپذیر در نظر گرفتهایم. در این معماری، بسیاری از هستهها و چیپلتها بهصورت سلسلهمراتبی به یکدیگر متصل شدهاند و در داخل هر چیپلت، هستهها با استفاده از اتصالات بسیار سریع ارتباط برقرار میکنند تا تأخیر کلی به حداقل برسد.”

پژوهشگران توصیه کردهاند که از حافظهی چند سطحی سلسلهمراتبی برای این طراحی استفاده شود که ممکن است در برنامهنویسی دستگاهها چالشهایی ایجاد کند.

در این ادامهی مقاله آمده است: “سلسلهمراتب حافظه شامل سه نوع حافظهی هسته (حافظهی کش)، حافظهی درون چیپلت و حافظهی بیرون چیپلت میشود. این سه نوع حافظه از نظر پهنای باند، تأخیر و مصرف انرژی متفاوت هستند. بهطور کلی در معماری چیپلت سلسلهمراتبی، چند هسته بههم متصل شدهاند و یک حافظهی کش را به اشتراک میگذارند که به این ساختار پاد گفته میشود. چند پاد یک چیپلت را تشکیل میدهند و چیپلتها بهصورت شبکهای به یکدیگر و به حافظهی مجتمع متصل میشوند و سپس با حافظهی بیرونی ارتباط برقرار میکنند.”

محققان افزودهاند: “طراحی دقیقی لازم است تا از ساختار سلسلهمراتبی بهطور کامل استفاده شود. بهرهگیری منطقی از پهنای باند حافظه برای توازن حجم کاری در ردهبندیهای مختلف پردازشی میتواند بهطور قابل توجهی کارایی سیستم چیپلت را افزایش دهد. طراحی مناسب منابع شبکهی ارتباطی میتواند تضمین کند که چیپلتها در استفاده از فضای حافظه بهخوبی همکاری خواهند کرد.”

نظرات کاربران